## IPB-AAC-LC-HE-ME

# AAC-LC AND HE-AAC AUDIO ENCODER

### **Overview**

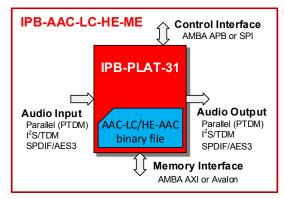

The AAC-LC and HE-AAC Audio Encoder (IPB-AAC-LC-HE-ME) is a software IP for encoding up to 6 audio channels in real-time. It is designed to run on our IPB-PLAT audio engine platform.

The IPB-AAC-LC-HE-ME software requires an instance of the IPB-PLAT audio engine platform named **IPB-PLAT-31**.

The user can upload the IPB-AAC-LC-HE-ME program using a hardware interface. The program can be configured, run and monitored by means of a configuration, control, and status register file, accessed by the same control interface.

The audio input and output interfaces include a native parallel interface. Other interfaces, such as, I<sup>2</sup>S/TDM and SPDIF/AES3 are also available.

#### **Features**

- MPEG2/4 AAC LC, HE-AAC v1, software employed Fraunhofer IIS high quality software which supports ISO/IEC 13818-7, ISO/IEC 14496-3 and Japanese ARIB standard

- Supported channel modes: mono, dual mono, stereo (2.0), 2.1, 3.0, 3.1, 4.0, 5.0, and 5.1

- Supported sampling rates: 8, 16, 22.05, 32, 44, 44.1 and 48 kHz

- Supports multiple audio streams limited to 6 audio channels in total (e.g. 3 stereo streams)

- Maximum 16-bit input audio resolution

- Requires 4.28 MB of external memory

- Configurable output latency useful to synchronize with other sources (e.g. video)

- Minimum latency: 1 frame for up to 2 channels,

2 frames for more than 2 channels per stream

- Software interface protocol for control, configuration and monitoring

- Parameter change while muting or repeating one frame

- Supported bitrate control modes: fixed framing, ABR and VBR

- Supported transport types: raw, ADTS, ADIF, LATM, and LOAS

- Real time operation @90 MHz for worst-case settings

Disclaimer: IPbloq reserves the right to modify the current technical specifications without notice

### **Benefits**

- Low operation frequency

- Low power consumption

- Optimizable to fulfill different design specifications

# **Block Diagram**

# Implementation Results(1)

Intel/Altera Cyclone-V

| ALMs   | Registers | DSPs | Memory<br>bits |

|--------|-----------|------|----------------|

| 24,100 | 24,100    | 29   | 1,559,000      |

#### Xilinx Spartan-6

| LUTs   | FFs    | DSPs | BRAM 18K |

|--------|--------|------|----------|

| 43,700 | 23,800 | 33   | 125      |

(1) Implementation results for other FPGAs or ASIC technologies can be provided upon request

#### **Deliverables**

- Program binary

- Software manual

- Hardware datasheet

- RTL or FPGA netlist

- Implementation constraints

# **Contact Information**

Web: www.ipbloq.com

Email: info@ipbloq.com

Address: Av. Reinaldo dos Santos, 23-4 Drt

2675-674 Odivelas

Portugal